TSMC has detailed its chip construction timeline at its 2022 TSMC Era Symposium.

The Taiwan-based chipmaker is introducing 3nm chips in the second one part of this 12 months and can convey 2nm generation to the arena level in 2025.

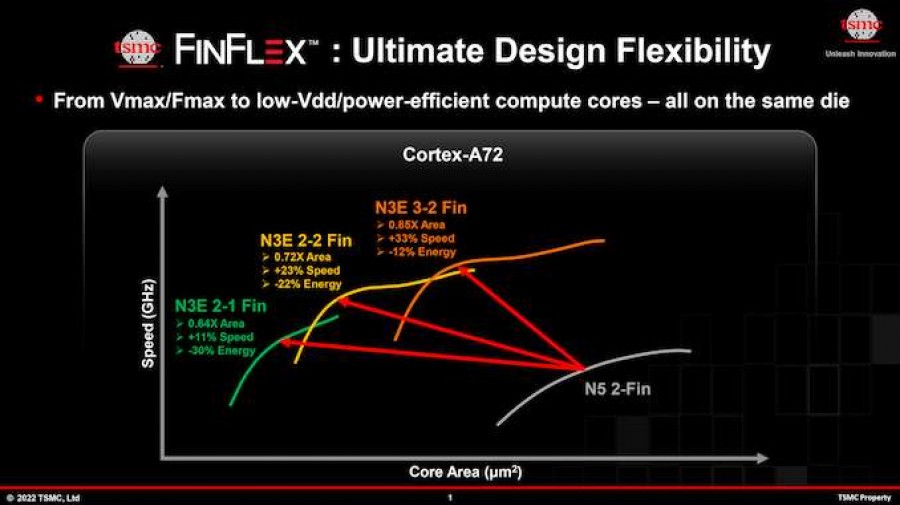

The 3nm node will are available in 5 tiers, each and every extra tough, extra transistor-dense, and extra environment friendly – N3, N3E (Enhanced), N3P (Efficiency Enhanced), N3S (Density Enhanced), and N3X (Extremely Prime Efficiency).

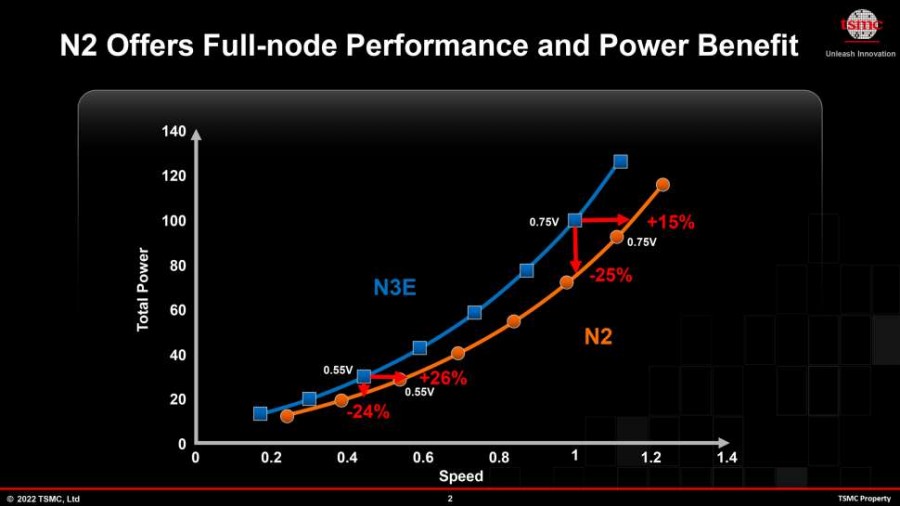

As for the 2nm node, it’ll spice up efficiency by means of 10% to fifteen % on the identical energy draw, and convey a 25% to 30% decrease intake on the identical frequency and transistor depend, in comparison to the N3E node. N2 will increase chip density over N3E by means of 1.1x.

TSMC offered GAAFETs (gate-all-around field-effect transistors). The brand new nanosheet transistors will build up efficiency consistent with watt by means of lowering resistance.

In the meantime, Samsung Foundry can even begin mass-producing 3nm chips in 2022, however plans to start generating 2nm chips in 2025, as smartly.